ISA

명령어 집합(Instructino Set) 또는 명령어 집합 구조(Instruction Set Architecture)는 마이크로프로세서가 인식해서 기능을 이해하고 실행할 수 있는 기계어 명령어를 말한다.

마이크로프로세서마다 기계어 코드의 길이와 숫자코드가 다르다

명령어의 각 비트는 기능적으로 분할하여 의미를 부여하고 숫자화한다.

아래 그림을 보면 응용 어플리케이션에서부터 여러 단계를 거쳐 소프트웨어에서 하드웨어로 넘어가게 된다

이때 소프트웨어에서 하드웨어로 넘어가는 단계에서 중재역할을 해주는 것이 ISA이다.

ISA는 최하위 레벨의 프로그래밍 인터페이스로 프로세서가 실행할 수 있는 모든 명령어들을 포함한다.

명령어 집합, 곧 명령어 집합 구조는 자료형, 명령어, 레지스터, 어드레싱 모드, 메모리 구조, 인터럽트, 예외 처리, 외부 입출력을 포함한 프로그래밍 관련 컴퓨터 아키텍처의 일부이다

명령어 집합 구조를 물리적으로 구현하는 방법을 마이크로아키텍처 혹은 컴퓨터 조직이라고 하며, 같은 명령어 집합 구조를 서로 다른 마이크로아키텍처로 구현하기도 한다.

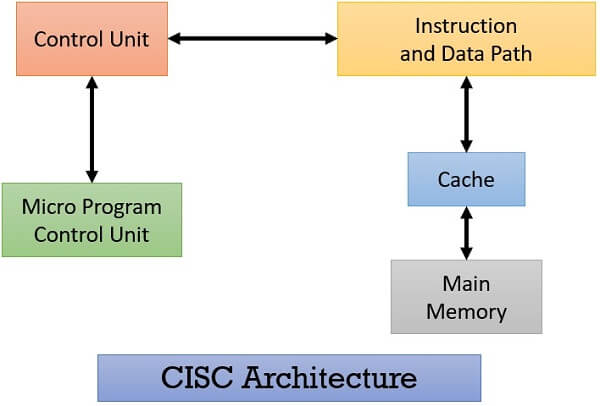

CISC

Complex Instruction Set Computer

복잡한 명령어 집합을 갖는 CPU 아키텍처이다.

명령어가 복잡하기 때문에 명령어를 해석하는데 시간이 오래 걸리며, 명령어 해석에 필요한 회로도 복잡하다.

만약 데이터나 주소값이 필요하다면 명령어 길이를 늘려 해결한다. 복잡하다는 편견과 달리 CSIC구조는 명령어 세트 설계가 바이트 단위로 깔끔한 편이다.

풍부한 어드레싱 기능을 갖추고 있어 명령의 직교성이 좋으며, 어느 어드레싱 모드에서도 임의의 연산을 수행할 수 있다.

흔히 비파이프라이닝 방식을 사용하는데, 이 방식은 명령어를 하나씩 처리하는 방식으로 한 명령어가 끝나야 다음 명령어를 처리하므로 명령어를 쪼개서 한번에 여러개를 동시에 처리하는 파이프라이닝 방식에 비해 비효율적이다.

현재는 거의 모습을 찾아 볼 수 없다.

CISC를 사용한 CPU중에서는 AMD64x86, M68K, 68xx 등이 있다.

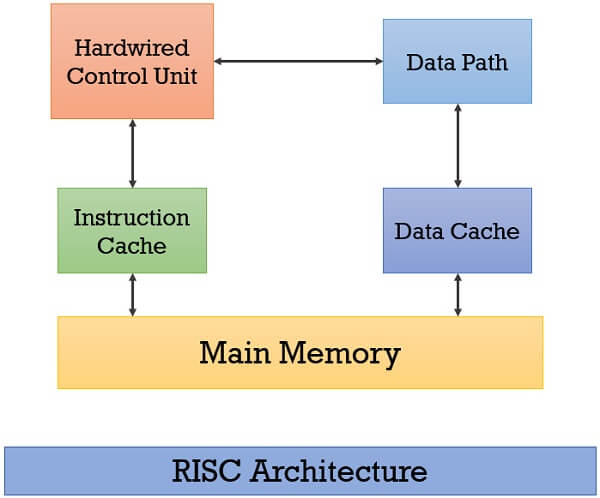

RISC

Reduced Instruction Set Computer

CPU명령어의 개수를 줄여 하드웨어 구조를 좀 더 간단하게 만드는 방식

마이크로프로세서를 설계하는 방법 중 하나이다.

CISC CPU에는 프로그래밍을 돕기 위한 많은 수의 명령어와 주소 모드가 존재 했지만 그 중에서 실제로 쓰이는 명령어는 몇 개 되지 않는 다는 사실을 바탕으로 적은 수의 명령어만으로 명령어 집합을 구성하였다.

그래서 RISC는 CISC보다 구조가 더 단순하고 복잡한 연산도 적은 수의 명령어들을 조합하는 방식으로 수행이 가능하다.

그리고 CISC CPU에 소프트웨어적으로 적재된 내부 명령어들을 하드웨어적으로 구성하여 제어기가 제거된 부분에 프로세서 레지스터 배읔와 캐스를 둔다. 이렇게 함으로써 CPU가 상대적으로 느린 메인 메모리에 접근하는 횟수를 줄여주어 파이프라이닝 등 시스템 수행속도가 전체적으로 향상된다.

RISC는 대부분의 현대 프로세서 디자인에 채택되고 있고, 또 비교적 전력 소모가 적기 때문에 임베디드 프로세서에서도 채택되고 있다.

RISC를 사용한 CPU중에서는 AArch64 ARM, RISC-V, MIPS 등이 있다.

| CISC | RISC | |

| 구조 | 복잡한 구조 | 단순한 구조 |

| 구성 | 복잡하고 많은 명령어 | 간단하고 최소 명령어 |

| 명령어 길이 | 다양한 길이 | 고정된 길이 |

| 레지스터 | 적음 | 많음 |

| 속도 | 느림 | 빠름 |

| 용도 | 개인용 컴퓨터 | 서버, 워크스테이션 |

'Study > Architecture' 카테고리의 다른 글

| Performance (0) | 2023.03.27 |

|---|---|

| 컴퓨터 구조 분야의 8가지 위대한 아이디어 (0) | 2023.03.10 |